Контролепригодная схема матричного двоичного умножителя

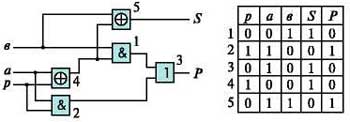

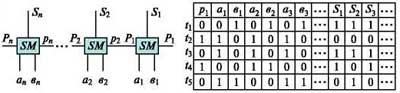

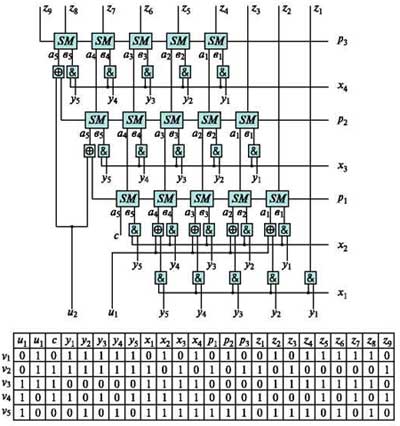

Проектирование контролепригодных цифровых ИС с регулярной структурой, к которым относятся сумматоры, умножители, делители, различные схемы памяти, значительно проще, чем ИС с нерегулярной структурой. Контролепригодная схема однотактного матричного двоичного умножителя, обладающая проверяющим тестом длины 6 относительно ее одиночных константных неисправностей независимо от ее размерности, имеет существенный недостаток - значительный объем аппаратных средств, необходимый для ее реализации. Этого недостатка лишена рассматриваемая оригинальная контролепригодная функционально-логическая схема однотактного матричного двоичного умножителя, обладающая проверяющим тестом длины 5. Основу новой схемы составляют слои одноразрядных сумматоров, объединенных в пределах каждого слоя в сумматор параллельного действия с последовательным переносом. При этом построение контролепригодной схемы одноразрядного сумматора, лежащей в основе многоразрядного сумматора каждого слоя, базируется на представлении функции суммы S в форме полинома Жегалкина, а функции переноса Р - в "смешанной" форме (специфика функции Р допускает такое представление): S = а ? b ? p; Р = (а•b ? b•p) v a-p = b•(a ? p) v a-p, где а и b - значения исходных одноразрядных операндов, p и Р - значения входного и выходного сигналов переноса, соответственно, S - значение сигнала суммы, ? - символ сложения по mod 2, v - символ дизъюнкции.  Рис.1. Контролепригодная схема одноразрядного сумматора Контролепригодная логическая схема одноразрядного сумматора, реализованная по приведенным формулам, показана на рис.1. Проверяющий тест для этой схемы относительно всех одиночных константных неисправностей содержит 5 векторов и описывается таблицей, представленной на рис. 1. Обнаружение отмеченных неисправностей этой схемы происходит следующим образом. Тестовые векторы 1, 2, 4 и 5 из таблицы рисунка 1 обнаруживают все одиночные константные неисправности данной схемы, кроме одиночной неисправности типа "константа 1" на том входе конъюнктора 2, который связан с внешним входом р. Эту неисправность обнаруживает тестовый вектор 3. Контролепригодная схема n-разрядного (где n - натуральное число) двоичного сумматора каждого слоя рассматриваемого матричного умножителя получается из n контролепригодных схем полного одноразрядного сумматора обычным путем, т.е. соединением выхода переноса i-й схемы с входом переноса (i+ 1 )-й схемы, где 1 ? i? n - 1. Эта схема приведена на рис.2.  Рис.2. Контролепригодная схема n-разрядного сумматора Проверяющий тест Т для контролепригодной схемы n-разрядного двоичного сумматора относительно всех ее одиночных константных неисправностей состоит из двух частей Т = Т1 Т2 и строится следующим образом: • часть Т1 содержит три тестовых вектора t1, t2, f3, которые образуются путем простой итерации соответственно первого, второго и третьего тестовых векторов из таблицы рис. 1 для всех разрядов; Тест Т описывается таблицей рис. 2. Контролепригодная функционально-логическая схема однотактного n x m-разрядного матричного умножителя (где n - число разрядов множимого, m - число разрядов множителя) для случая n = 5, m = 4 приведена на рис. 3. Эта схема, как и схема обычного 5х4-разрядного матричного умножителя, содержит три слоя сумматоров и четыре слоя конъюнкторов. Однако, как уже отмечалось, схемы сумматоров реализованы по приведенным выше формулам.  Рис. З. Контролепригодная схема 5х4-разрядного матричного умножителя Помимо этого, рассматриваемая схема содержит шесть дополнительных двухвходовых элементов "исключающее ИЛИ" и два дополнительных входа u1, u2. При этом в рабочем режиме на входы с, u1, u2, p1, р2, p3 подаются сигналы логического "0". Проверяющий тест для этой схемы относительно всех ее одиночных константных неисправностей содержит 5 векторов и описывается таблицей рис. 3. При подаче на входы схемы тестовых векторов из таблицы (см. рис. 3) в последовательности v1 v2, v3 v4, v5 на входы сумматора первого слоя поступят тестовые векторы из таблицы рис.2 в последовательности tb t2, t3, t5, f4; на входы сумматора второго слоя - тестовые векторы из таблицы рис. 2 в последовательности t2, t1, t3, t5, t4; на входы сумматора третьего слоя - тестовые векторы из таблицы рис. 2 в последовательности t1, t2, t3, t5, t4, т.е. обеспечивается подача на входы n-разрядного сумматора каждого слоя проверяющего теста этого сумматора относительно одиночных константных неисправностей. При этом также обеспечивается подача на входы каждого слоя конъюнкторов их проверяющих тестов и подача на входы дополнительных элементов "исключающее ИЛИ" проверяющих тестов этих элементов. Синтез тестовой последовательности для рассматриваемой контролепригодной схемы матричного двоичного умножителя может быть осуществлен на основе комбинации формальных и эвристических методов. Сначала строится проверяющий тест для схемы одноразрядного сумматора с помощью формальных методов (например, с помощью D- и PODEM-алгоритмов), а затем на основе этого теста поэтапно проводится построение общей тестовой последовательности для схемы матричного умножителя с помощью эвристических методов. Легко видеть, что в общем случае, т.е. когда nиm - произвольные натуральные числа, контролепригодная функционально-логическая схема однотактного матричного умножителя содержит m-1 сумматоров с последовательным переносом, m слоев конъюнкторов, а также п+m-3 дополнительных двухвходовых элементов "исключающее ИЛИ". Число дополнительных входов при этом не изменится и останется равным двум. Проверяющий тест для общего случая также содержит 5 векторов и строится следующим образом: • на каждый вход yj подается последовательность 1, 1, 0, 1, 0, если j - нечетное число, и последовательность 1, 1, 0, 0, 1, если j- четное число (j принадлежит {1, 2,..., n}); Схема одноразрядного сумматора, лежащая в основе рассматриваемой контролепригодной схемы матричного двоичного умножителя, легко преобразуется в схему, отличающуюся от схемы на рис. 1 только тем, что логические элементы 1, 2, 3 последней заменены логическими элементами "И-НЕ". Проверяющий тест контролепригодной схемы матричного умножителя, которая получается в результате данного преобразования схемы одноразрядного сумматора, останется прежним. При этом полученная контролепригодная схема в общем случае требует для своей реализации значительно меньших аппаратных затрат, чем более ранняя схема. Дело в том, что одноразрядный сумматор, лежащий в основе этой схемы, требует для своей реализации девять двухвходовых элементов "И-НЕ", а одноразрядный сумматор, лежащий в основе полученной схемы - два двухвходовых элемента "исключающее ИЛИ" и три двухвходовых элемента "И-НЕ". В случае использования биполярной технологии (в частности, ТТЛ) логический элемент "И-НЕ" может быть реализован схемой, содержащей два биполярных транзистора и два резистора. Элемент "исключающее ИЛИ" в этом случае может быть реализован схемой, содержащей всего три биполярных транзистора и два диода. Другими словами, здесь схемотехническая сложность реализации элемента "исключающее ИЛИ" практически равна схемотехнической сложности реализации элемента "И-НЕ". Известна также простая реализация элемента "исключающее ИЛИ" на основе КМОП-техноло-гии.

| |||||||||||||||||||||